Despite widespread frustration with legacy electronic design automation tools, startups repeatedly fail to disrupt the Cadence-Synopsys-Mentor stronghold. The real barrier isn't technology but an intricate web of fab certifications and process complexity that protects incumbents. Emerging players now pursue survival through complementary tools while navigating acquisition traps and legal minefields.

Every chip designer has a horror story about their electronic design automation (EDA) tools. The crashes. The prehistoric interfaces. The glacial performance. Yet despite decades of complaints about Cadence, Synopsys, and Mentor Graphics (now Siemens EDA), no startup has successfully challenged this $14 billion oligopoly. The reason reveals the brutal realities of semiconductor power dynamics.

"Startups either get acquired for less than $500M or get sued into oblivion by major EDA companies," observes industry commentator Zach. This pattern has held for nearly 20 years: Xoomsys (parallel SPICE simulators, 2007), Extreme DA (multi-core timing analysis, acquired by Synopsys 2011), and Rocketick (RTL simulation, acquired by Cadence 2016) all fell to the same fate.

The Certification MoAT

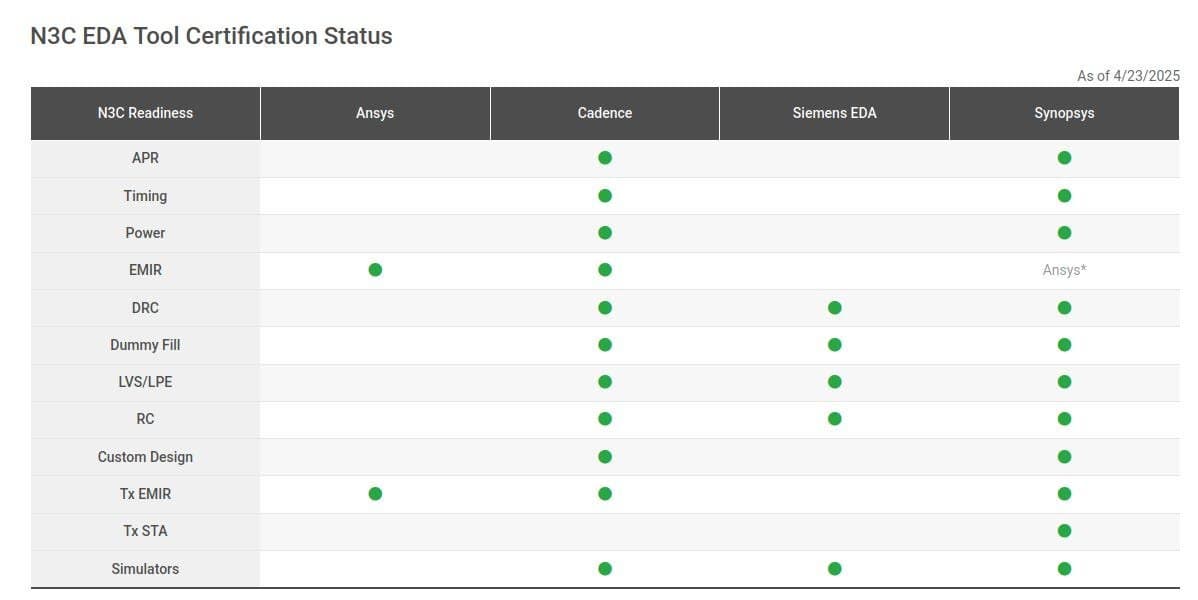

At the heart of the challenge lies TSMC's "EDA Alliance" – an exclusive club certifying tools for cutting-edge nodes like 3nm. With mask sets costing millions and production runs demanding perfection, designers won't risk uncertified tools. As Zach notes: "Even Siemens, the world's third-largest EDA vendor, lacks full certification coverage for TSMC's 3nm process."

Fab certification creates a vicious cycle:

- Process complexity: Modern 2nm nodes require tools handling quantum effects and atomic-scale variations – exponentially harder than 28nm-era development

- Risk aversion: Fabs prioritize stability with established partners over startup experimentation

- Scale barriers: Qualifying tools across multiple foundries (TSMC, Samsung, Intel) demands resources only giants possess

The Complementary Tool Gambit

Current startups like Partcl (GPU-accelerated placement) and Silimate (AI-powered PPA prediction) pursue a workaround: targeting non-signoff workflows where speed outweighs certification. These tools assist exploration and iteration without replacing the certified final signoff suite.

graph LR

A[Startup Tool] --> B(Design Exploration)

A --> C(Prototype Validation)

D[Cadence/Synopsys] --> E(Final Signoff)

But this strategy has limitations:

- Narrow market: Only large firms like NVIDIA or Apple can afford redundant toolchains

- Acquisition bait: Successful innovations become takeover targets (Extreme DA, Rocketick)

- Legal vulnerability: Patent lawsuits from incumbents drain startup resources

Breaking the Mold

For true disruption, startups must eventually conquer the certification hurdle. This demands either:

- Regulatory intervention challenging anti-competitive practices

- Alliances with second-tier fabs seeking differentiation

- Radical technology shifts like open-source EDA gaining fab acceptance

As process nodes approach atomic scales, the industry's reliance on legacy tools becomes increasingly unsustainable. The startups that survive acquisition overtures and legal warfare while solving real designer pain points may yet crack the fortress – no marriage to TSMC founder Morris Chang's daughters required.

Source: Adapted from Why is it so hard for startups to compete with Cadence? on zach's tech blog

Comments

Please log in or register to join the discussion