Industry sources confirm both AMD's Zen 6 'Olympic Ridge' and Intel's Nova Lake-S desktop processors face substantial delays, shifting from late 2026 to early 2027 launches amid semiconductor production constraints and AI-driven resource reallocation.

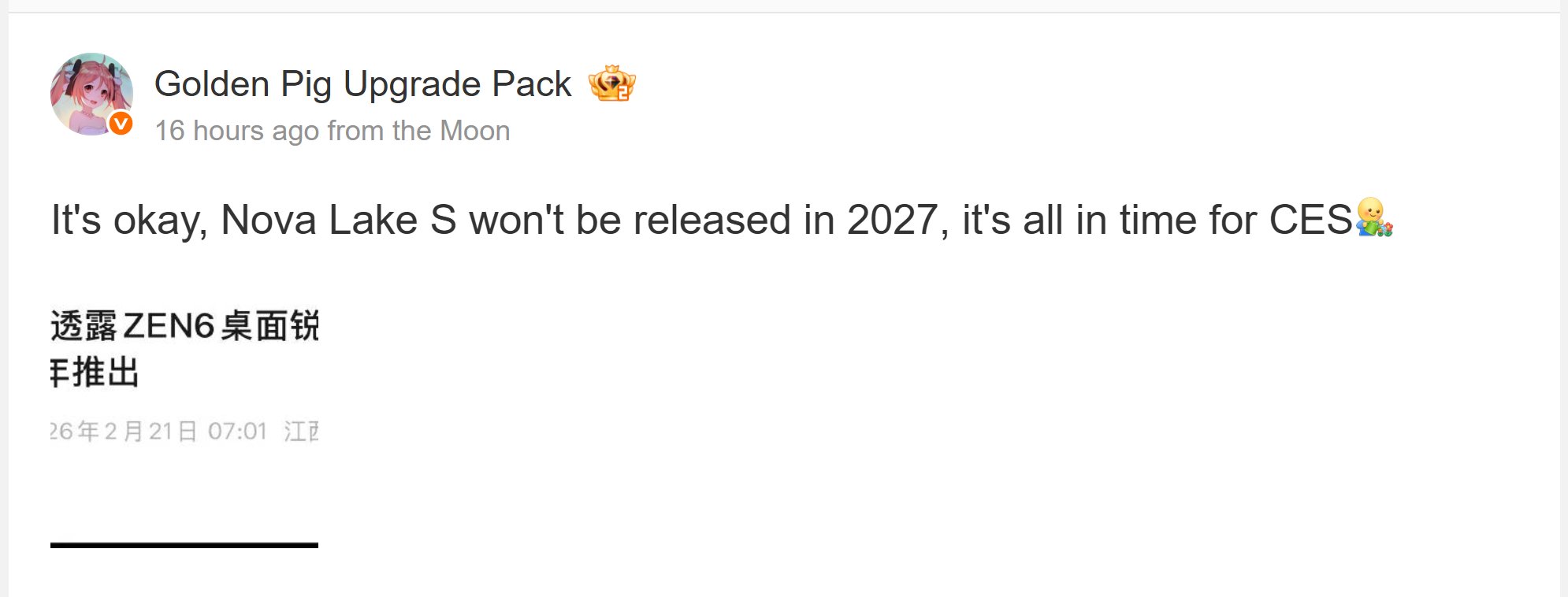

Semiconductor manufacturing bottlenecks and strategic resource shifts toward AI-optimized silicon have forced major schedule adjustments for next-generation desktop processors from industry leaders. Verified industry sources including Benchlife and Golden Pig Upgrade indicate both AMD's Zen 6 architecture (codenamed Olympic Ridge) and Intel's Nova Lake-S desktop processors will now launch at CES 2027, representing a 6-12 month delay from original roadmaps.

Technical Specifications Under Constraints

Despite the delays, architectural advancements remain significant. AMD's Zen 6 design introduces a fundamental shift with 12-core Compute Chiplet Dies (CCDs), doubling the current 6-core CCD configuration. This enables 24-core mainstream desktop processors without multi-CCD latency penalties, a first for Ryzen consumer chips. Cache hierarchies are also undergoing redesigns to accommodate the increased core density while maintaining clock speed parity with Zen 5.

Intel's Nova Lake counters with a hybrid architecture scaling to 52 cores on desktop silicon, supported by a massive 288MB of bundled Last-Level Cache (bLLC). This cache configuration directly targets AMD's 3D V-Cache technology, providing competitive latency-sensitive performance without specialized packaging. Early engineering samples suggest Nova Lake's Lion Cove P-cores deliver 25% higher IPC than current Arrow Lake designs, while Skymont E-cores see even more substantial gains.

Manufacturing and Supply Chain Pressures

The delays stem from convergent industry pressures:

- Node Allocation Conflicts: Both companies prioritize high-margin data center products amid AI infrastructure demand. Intel confirmed shifting 30% of its Intel 20A production capacity from consumer to server chips in Q1 2024.

- Material Cost Inflation: DRAM prices have increased 200% year-over-year, with NAND flash and GPU components seeing 40-60% cost hikes. These constrain budget allocations for consumer R&D.

- Packaging Bottlenecks: TSMC's CoWoS advanced packaging capacity remains allocated to AI accelerators through 2026, delaying complex consumer chipset development.

Market Implications

The schedule shift creates ripple effects across the computing ecosystem:

- Extended Product Lifecycles: Current Zen 5 and Arrow Lake architectures will see refreshed models through 2026, with AMD confirming no interim desktop releases before Zen 6.

- Data Center Prioritization: Both companies will launch server variants (AMD's Zen 6-based Venice EPYC, Intel's Sierra Forest) in late 2026 as planned, widening the consumer/enterprise release gap.

- Pricing Pressure: Component cost inflation combined with constrained supply suggests 2027 flagship CPU pricing could exceed current generation by 15-20%.

- Competitive Dynamics: The compressed 2027 launch window sets up a direct architectural showdown. AMD's cache-optimized multi-core approach faces Intel's core-count advantage and new diode stacking techniques.

Industry analysts note these delays reflect structural realignment rather than technical failures. With AI infrastructure commanding 45% of leading-edge wafer starts and memory prices at historic highs, consumer silicon faces prolonged allocation challenges. The CES 2027 launches will showcase how both companies adapt architectures to these constraints while delivering generational performance gains exceeding 30%.

Comments

Please log in or register to join the discussion