Computer scientist Brad has created a hardware multiplication accelerator for vintage Intel 8086/8088 systems using a 1980s TRW MPY12HJ parallel multiplier chip, achieving 2.5x faster integer multiplication by offloading MUL instructions from the CPU.

A computer scientist and boating enthusiast known as @bradthx on X has built a hardware multiplication accelerator for Intel 8086 and 8088 PC systems that dramatically improves integer multiplication performance on these vintage computers.

The Problem with Vintage Multiplication

On the original 8088/8086 processors, multiplication was implemented as an iterative shift/add algorithm controlled by microcode. Brad explains that these early Intel CPUs calculated multiplication "the same way you would solve it on paper in binary." This approach meant that multiplication operations took "a crazy long time" compared to modern processors.

The fundamental issue was that the 8086's microcoded multiply loop was inherently slow, making integer multiplication one of the most performance-limiting operations on these classic systems.

The Solution: A 1980s Parallel Multiplier

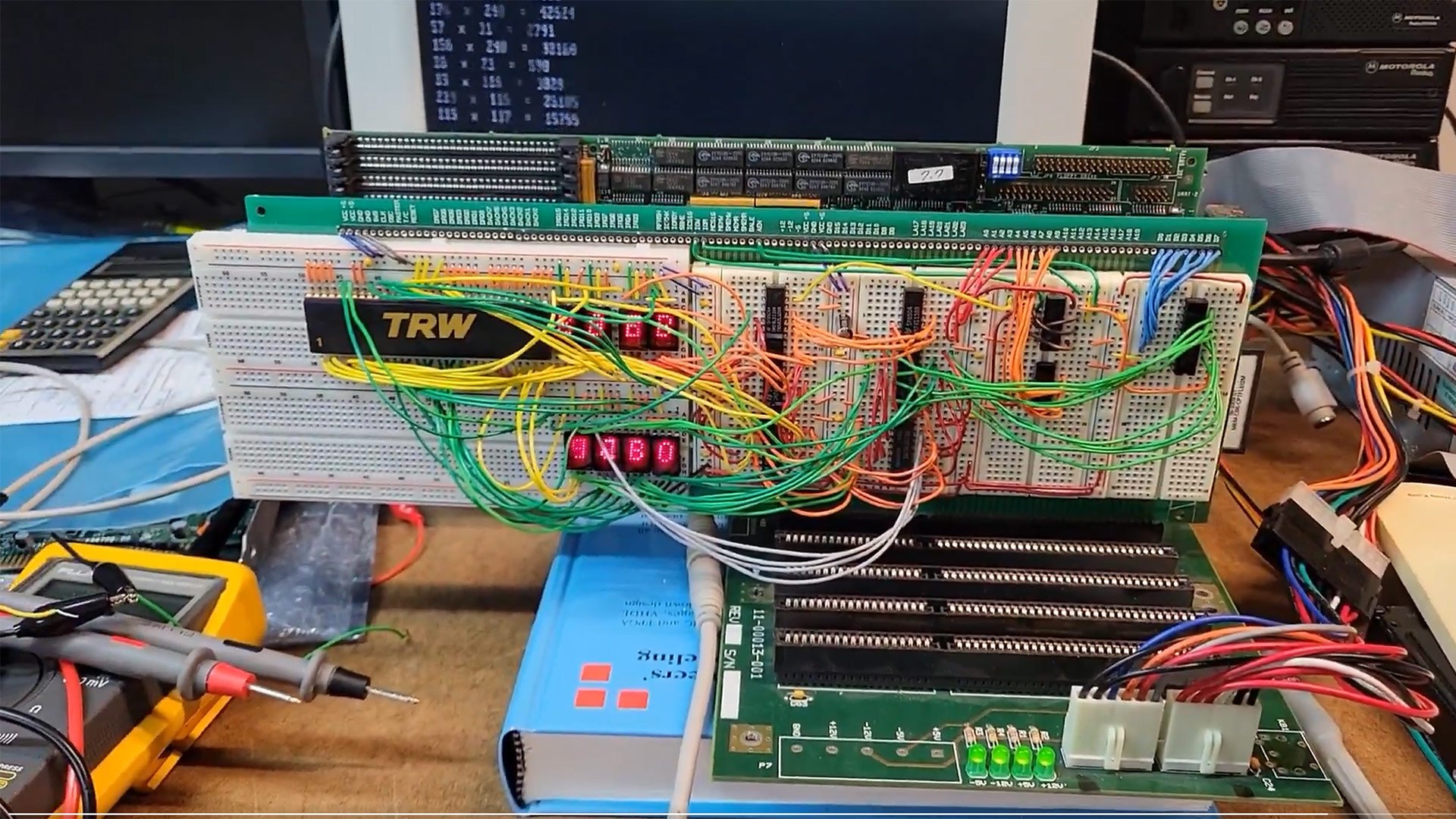

Brad's solution centers around the TRW MPY12HJ chip, a "12×12 parallel multiplier designed specifically for high-speed arithmetic operations" that was available in the late 1970s and early 1980s. This chip operates asynchronously without a clock, running as fast as bits can propagate through the silicon.

"It actually makes integer multiplication about 2.5× faster on early x86 systems," Brad notes. The key advantage is that the TRW multiplier is "orders of magnitude faster than the CPU's microcoded multiply loop."

How It Works

Because the TRW multiplier is so fast, it can calculate intercepted MUL instructions between two consecutive bus cycles. This means that placing the accelerator on an ISA card doesn't create a significant performance penalty, as Brad explains: "having it on an ISA card isn't a killer performance penalty."

Overall, the accelerator card achieves performance "about 2.5× faster than the CPU's built-in multiplier."

Technical Implementation

The accelerator is implemented as an ISA card, making it compatible with the open architecture that IBM introduced with the Model 5150 in 1981. This architecture would go on to define the PC industry and famously debuted ISA slots.

Brad's approach intercepts MUL instructions and redirects them to the hardware multiplier, effectively offloading this computationally intensive task from the CPU. The asynchronous nature of the TRW chip means it can complete calculations faster than the CPU could handle them through its microcoded approach.

Limitations and Practical Considerations

While the project is technically impressive, there are practical limitations. The accelerator won't work its magic on classic old applications unless you have access to the source code. Brad explains that "for anything that I build, I can use my own subroutine that uses this hardware multiplier instead of the internal x86 MUL instruction."

Pre-compiled applications aren't aware of the accelerator card and will continue to use the CPU's built-in multiplication instructions. This means the performance benefits are primarily available to custom software or applications that can be recompiled to take advantage of the hardware acceleration.

Why Build It?

Brad acknowledges the somewhat whimsical nature of the project in 2026: "This is obviously not necessary in 2026 lol, but was absolutely worth building."

The project demonstrates both the ingenuity of the retro computing community and the potential for hardware acceleration even on vintage systems. It also highlights how certain computational tasks that were bottlenecks on early processors could have been addressed with available technology at the time.

Demonstration

Brad has shared videos demonstrating the accelerator in operation. In one demonstration, the card is shown performing multiplication operations significantly faster than the CPU alone could manage. However, Brad notes that "printing the math to the display for demonstration is a huge bottleneck that slows it down," indicating that the actual computational speedup is even more dramatic than what's visible in the demonstration.

The project represents an interesting intersection of historical computing technology and modern maker culture, showing how vintage hardware can be enhanced with period-appropriate components to achieve performance improvements that were theoretically possible decades ago but rarely implemented in consumer systems.

Comments

Please log in or register to join the discussion