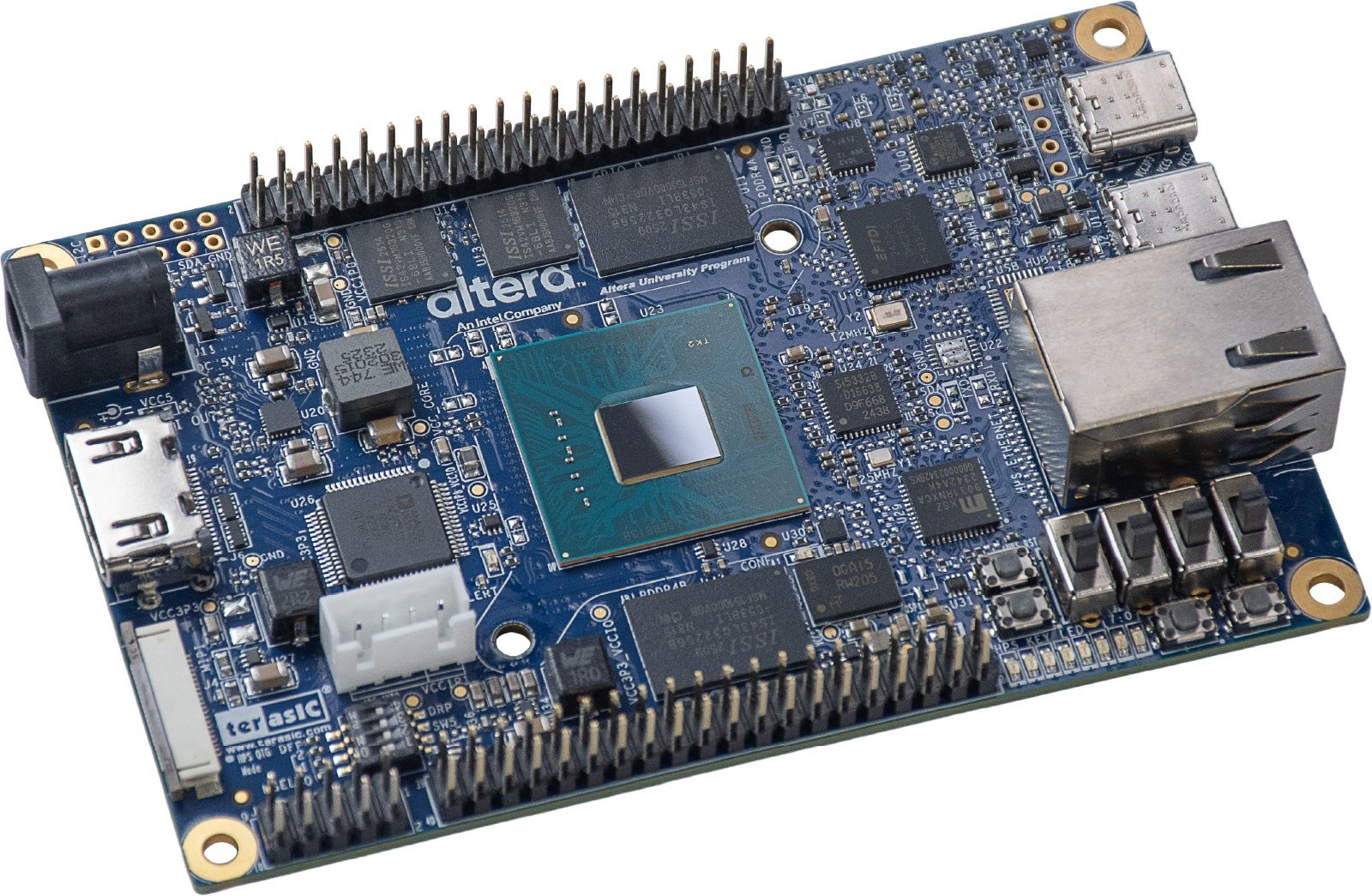

Terasic's DE25-Nano development board delivers next-gen Intel Agilex™ 5 FPGA performance with a 138K-logic element array, dual-cluster ARM Cortex processors, and 2GB LPDDR4 in the same footprint as its predecessor. Engineered for AI, embedded vision, and edge analytics, its production-ready I/O and daughter card ecosystem bridge prototyping to real-world deployment.

The edge computing landscape just gained a formidable contender. Terasic has launched the DE25-Nano development board, a significant evolution of its popular DE10-Nano that crams Intel's cutting-edge Agilex™ 5 FPGA technology into a palm-sized form factor. Targeting developers working on AI inference, real-time vision processing, and industrial control systems, this board represents a generational leap in embedded hardware capabilities while maintaining backward-compatible dimensions—enabling seamless upgrades for existing projects.

Hardware Revolution in Miniature

At its core, the DE25-Nano features an Agilex™ 5 FPGA with 138,000 logic elements—substantially outperforming prior generations in both computational density and power efficiency. Paired with 2GB of onboard LPDDR4 memory and Terasic's integrated USB-Blaster III programmer, it eliminates common prototyping bottlenecks. The heterogeneous processing architecture integrates a dual-cluster ARM Cortex-A76/A55 Hard Processor System (HPS), enabling complex software-hardware co-design workflows where FPGA-accelerated algorithms and application logic run in tandem.

Production-Ready Peripherals

What distinguishes the DE25-Nano from academic toys is its industrial-grade I/O suite:

- Vision & Display: Native HDMI and MIPI interfaces for camera input and display output

- Signal Acquisition: Integrated ADC for sensor data capture

- Expansion: 40-pin GPIO headers and HPS-FPGA shared memory channels

- Daughter Card Ecosystem: Compatibility with Terasic's accessory boards for rapid sensor/actuator integration

This versatility allows developers to transition prototypes directly to field-deployable solutions without redesigning core hardware—critical for robotics, medical devices, or automated inspection systems.

Why This Matters for Edge Innovation

The DE25-Nano arrives as edge AI workloads explode in complexity. Its Agilex™ 5 FPGA enables hardware-customizable accelerators for transformer networks or computer vision pipelines, while the ARM HPS handles OS and control logic. By retaining the DE10-Nano's form factor, Terasic ensures existing chassis and thermal solutions remain viable, reducing adoption friction. Educational institutions gain an affordable platform to teach FPGA co-processing, while enterprises leverage it for scalable edge deployments—proving that big compute no longer demands bulky hardware.

As one developer noted: 'This isn’t just an upgrade—it’s a paradigm shift for embedded R&D.' With Terasic’s mature tooling and community support, the DE25-Nano blurs the line between development board and deployment platform, accelerating the future of intelligent edge devices.

Source: Terasic DE25-Nano Product Page

Comments

Please log in or register to join the discussion