The upcoming Linux 7.1 kernel will include support for exposing AMD Zen 6's AVX-512 BMM instructions to virtualized guests, marking an important step in enabling next-generation vector processing capabilities in cloud and containerized environments.

The Linux kernel is preparing to support one of AMD's most anticipated architectural features with the upcoming Linux 7.1 release. A recently merged patch will enable the kernel's KVM (Kernel-based Virtual Machine) subsystem to properly advertise AVX-512 BMM (Bit Matrix Multiply) support to guest virtual machines running on AMD Zen 6 processors.

AVX-512 BMM represents a significant addition to AMD's instruction set architecture, focusing on matrix multiplication operations and bit manipulation capabilities. This instruction set extension is particularly relevant for workloads involving machine learning, cryptography, and other data-intensive operations that benefit from efficient bit-level processing.

The Technical Implementation

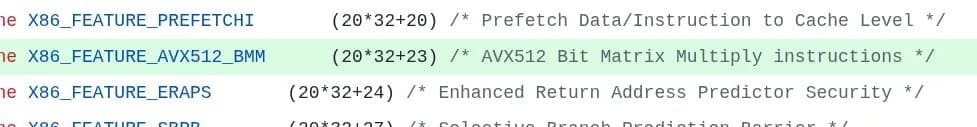

The patch, which has been queued into the kvm-x86 subsystem, adds support for exposing AVX-512 BMM capabilities through CPUID leaf 0x80000021_EAX[23]. This follows the established pattern for how KVM handles Advanced Vector Extensions instructions, requiring no special intercept controls or additional virtualization overhead.

As the patch notes explain: "KVM: x86: Advertise AVX512 Bit Matrix Multiply (BMM) to userspace. Advertise AVX512 Bit Matrix Multiply (BMM) and Bit Reversal instructions to userspace via CPUID leaf 0x80000021_EAX[23]. This feature enables bit matrix multiply operations and bit reversal. Like most AVX instructions, there are no intercept controls for individual instructions, and no extra work is needed in KVM to enable correct execution of the instructions in the guest."

This approach ensures that guest operating systems can detect and utilize AVX-512 BMM capabilities just as they would on bare metal hardware, without requiring any special virtualization considerations.

Context and Development Timeline

The AVX-512 BMM instructions were first confirmed through AMD's Zen 6 ISA patches for GNU Binutils last year. This was subsequently validated by compiler support patches for both GCC (Znver6) and LLVM/Clang, ensuring that software developers would have the necessary toolchain support for targeting these new instructions.

With the KVM support now in place, the complete software stack for Zen 6's AVX-512 BMM is falling into place. The patch is expected to be submitted as part of the broader KVM changes when the Linux 7.1 merge window opens later this month.

Implications for Virtualization

The inclusion of AVX-512 BMM support in KVM has significant implications for cloud providers and enterprise virtualization environments. Organizations running virtualized workloads on AMD Zen 6 hardware will be able to fully leverage these new instructions without performance penalties or compatibility issues.

This is particularly important for cloud-native applications and containerized workloads that rely on efficient vector processing. The ability to expose these capabilities to guests means that virtual machines can take full advantage of the hardware acceleration provided by AVX-512 BMM, potentially improving performance for machine learning inference, database operations, and other compute-intensive tasks.

Looking Ahead

As AMD's Zen 6 processors begin to ship and Linux 7.1 becomes available, we can expect to see increased adoption of AVX-512 BMM in both native and virtualized environments. The seamless integration of these instructions into the virtualization layer demonstrates the maturity of the Linux kernel's virtualization support and AMD's commitment to providing comprehensive instruction set extensions.

The patch represents a small but crucial piece of the puzzle in enabling next-generation computing capabilities in virtualized environments, ensuring that the benefits of AMD's architectural innovations can be fully realized regardless of deployment model.

Comments

Please log in or register to join the discussion