A 16-line patch, primarily consisting of comments, adjusts the Linux kernel's menu governor to add a 25% safety margin, reducing wakeup latency from ~150µs to ~30µs on Sapphire Rapids and newer Xeon platforms without impacting power efficiency.

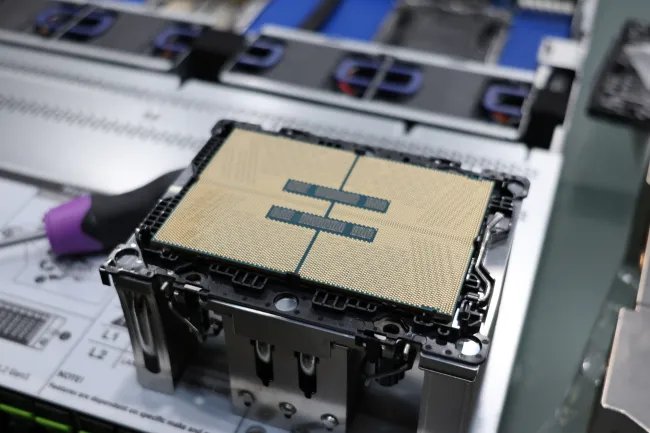

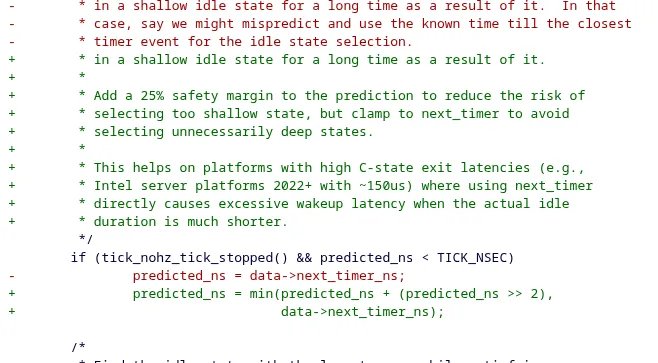

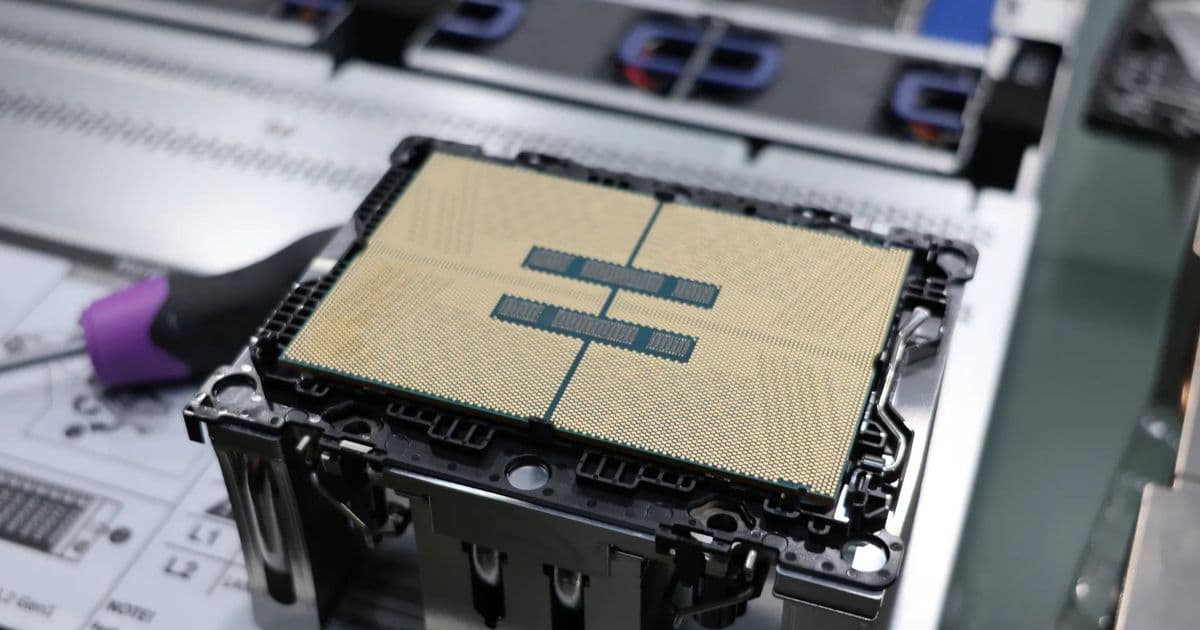

A seemingly minor adjustment to the Linux kernel's CPU idle governor is delivering a dramatic performance improvement for latency-sensitive workloads on modern Intel Xeon server platforms. A patch submitted to the Linux kernel mailing list by Wind River cloud engineer Ionut Nechita targets the menu governor, a component responsible for selecting the most efficient CPU power state (C-state) when a processor is idle. The change, which modifies just one line of actual code within a 16-line patch, addresses a critical inefficiency introduced with Intel's Sapphire Rapids architecture and persisting through the latest Granite Rapids processors.

The core issue stems from the interaction between the Linux kernel's NOHZ_FULL configuration (which disables the periodic timer tick on idle CPUs) and the menu governor's prediction logic. On modern Xeon servers, the governor was selecting excessively deep package C-states (like PC6) for idle periods that were actually quite short. This decision, while theoretically optimal for power savings, incurred a severe penalty due to the complex exit latency of these deep states on new hardware. The problem is multifaceted, driven by DDR5 power management overhead, the per-tile power gating architecture of modern Xeon CPUs, CXL link restoration times, and other server-specific complexities.

The result was a wakeup latency of approximately 150 microseconds on affected platforms, a stark contrast to the 12-21µs latency seen on previous-generation Ice Lake and Skylake Xeon processors. For latency-sensitive applications such as high-frequency trading, real-time analytics, and certain database operations, this 10x increase in latency can significantly degrade performance.

The proposed fix is elegantly simple. Instead of using the predicted idle duration (next_timer_ns) directly when the tick is already stopped, the patch introduces a 25% safety margin. This adjustment makes the governor more conservative, protecting against the selection of excessively deep C-states while still avoiding the selection of unnecessarily shallow states. The logic is clamped to next_timer_ns to ensure the governor doesn't overshoot and choose a state deeper than necessary for the predicted idle time.

The benchmark results, as detailed in the patch submission, are compelling. Testing on an Intel Xeon Sapphire Rapids platform using the qperf tcp_lat benchmark showed a dramatic improvement:

- Before patch: 151µs average latency

- After patch: ~30µs average latency

- Improvement: A 5x reduction in wakeup latency

Critically, the patch demonstrates no performance regression on older platforms. Testing on Ice Lake and Skylake Xeon processors showed identical latency measurements before and after the change (12µs and 21µs, respectively), confirming the fix is specific to the problematic behavior of newer architectures.

Furthermore, the power efficiency impact is negligible. Power consumption testing during mixed workloads showed less than a 1% difference in package power, a figure well within the margin of measurement noise. This confirms that the 25% safety margin successfully mitigates the latency penalty without sacrificing the power efficiency gains that deep C-states provide.

While the initial patch submission includes benchmark data only for Sapphire Rapids, the underlying architectural changes that cause high C-state exit latency are shared with subsequent generations. Therefore, the performance benefit is expected to extend to newer Xeon platforms like Granite Rapids. The patch is currently under review on the Linux kernel mailing list, and if accepted, will be integrated into future kernel releases, providing a significant performance uplift for data centers running latency-critical applications on modern Intel server hardware.

The patch's minimal code footprint underscores the precision of the fix. It highlights how a deep understanding of hardware-software interaction can yield outsized performance gains. This is a classic example of a targeted optimization that addresses a specific hardware quirk introduced by a new generation of processor architecture, demonstrating the ongoing need for close collaboration between chip manufacturers and the open-source software community to unlock full platform potential.

For data center operators and cloud providers, this patch represents a low-risk, high-reward update. It can be deployed via a standard kernel update, requiring no hardware changes or application modifications. The result is a more responsive system for workloads that are sensitive to I/O and context-switch latency, directly improving application performance and potentially reducing the need for over-provisioning hardware to meet latency Service Level Agreements (SLAs).

Comments

Please log in or register to join the discussion