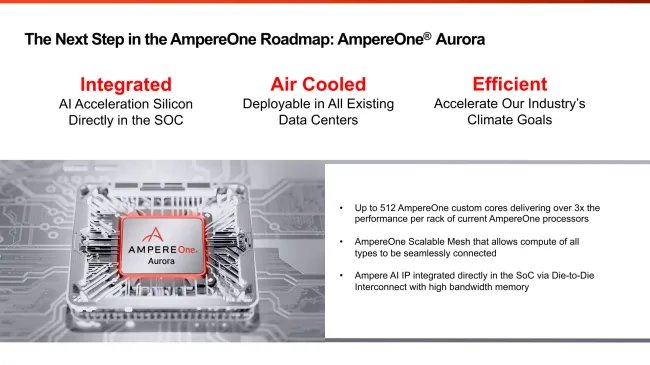

LLVM/Clang's latest Git commit introduces 'Ampere1C' CPU core support, signaling progress toward Ampere Computing's 512-core AmpereOne Aurora server processors based on Armv9.2 with SVE2 extensions.

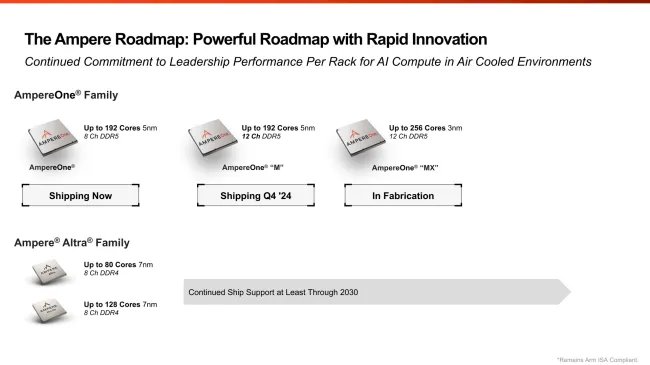

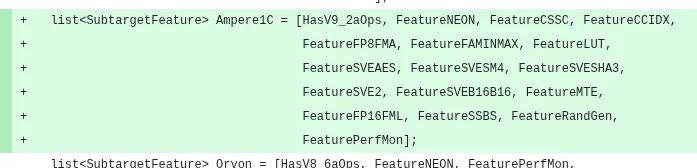

The LLVM/Clang compiler stack has merged support for Ampere Computing's next-generation "Ampere1C" CPU core ahead of the LLVM 22 release scheduled for Q1 2026. This addition, committed to LLVM Git, marks the fourth AmpereOne variant recognized by open-source compilers following Ampere1 (original AmpereOne), Ampere1A (AmpereOne M), and Ampere1B (anticipated AmpereOne MX). Technical annotations confirm Ampere1C implements Arm's v9.2 architecture with Scalable Vector Extensions v2 (SVE2) support, positioning it as the foundation for AmpereOne Aurora—Ampere's planned 512-core server processor.

Roadmap Implications

Ampere Computing's publicly disclosed roadmap places Aurora after the 256-core AmpereOne MX, targeting a substantial core-count leap. Industry observers questioned Aurora's viability following SoftBank's 2025 acquisition of Ampere Computing and the limited market penetration of current AmpereOne hardware. Oracle Cloud remains the sole major adopter of AmpereOne M processors, with no retail availability. The compiler integration suggests Aurora development continues despite these challenges. Architectural documentation indicates Ampere1C inherits Ampere's consistent 3.3GHz base clock philosophy while adding Armv9.2 features like memory tagging (MTE) and enhanced virtualization (RME), which could yield 15-20% IPC gains over AmpereOne's Armv8.6 implementation.

Performance Expectations

While benchmark data for Ampere1C remains unavailable, its SVE2 implementation warrants attention. SVE2 doubles vector width flexibility versus NEON and introduces data-centric optimizations critical for AI workloads. Comparing Ampere Altra Max's 128-core Neoverse-N1 performance (2.8GHz, 250W TDP), Aurora's 512-core design could potentially quadruple throughput within a 350W envelope assuming similar per-core efficiency. Memory bandwidth will be decisive; current AmpereOne platforms utilize 12-channel DDR5-4800 delivering 460GB/s—Aurora would require quad-socket configurations or next-gen memory to avoid bottlenecks.

Build Considerations

Homelab enthusiasts should note Aurora's compatibility horizon:

- Compiler Requirements: LLVM Clang ≥22 or GCC ≥14 (pending support)

- OS Support: Linux 6.8+ for Armv9.2/SVE2 enablement

- Power Planning: Expect 300W+ TDP per socket; redundant 1600W+ PSUs recommended

- Cooling: Industrial-grade air or liquid cooling required for sustained boost clocks

Until Aurora ships, Ampere Altra Max remains the accessible choice for ARM64 builds, with System76's Thelio Astra and ASRock's 4U-2X2TF offering retail availability. AmpereOne M's cloud-exclusive status limits benchmarking, but Oracle's OCI instances show 40% higher HPL efficiency than x86 competitors at similar core counts. When Aurora arrives, its 512-core design could challenge AMD EPYC Bergamo in density-sensitive workloads, provided Ampere addresses platform accessibility.

Compiler integration typically precedes hardware launch by 6-12 months, signaling potential late 2026 availability. Developers should test SVE2 optimizations now using QEMU emulation with -cpu ampere1c flags. For ongoing updates, track Ampere's developer portal.

Comments

Please log in or register to join the discussion