Marvell acquires XConn Technologies, gaining advanced PCIe/CXL switching technology including 256-lane PCIe Gen5 switches with CXL 2.0 support and upcoming PCIe Gen6/CXL 3.1 solutions.

Marvell Technology has announced the acquisition of XConn Technologies, a strategic move expanding its portfolio in PCIe switching and Compute Express Link (CXL) technologies. This acquisition provides Marvell with critical switching IP addressing two converging infrastructure markets.

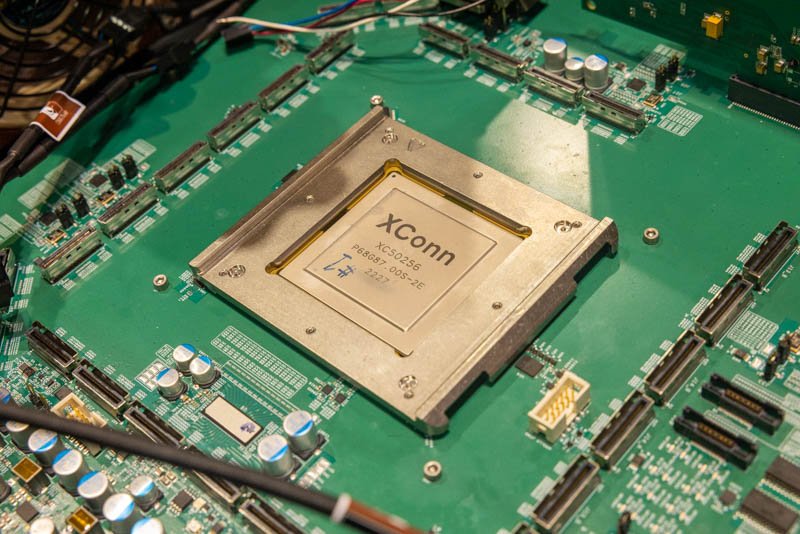

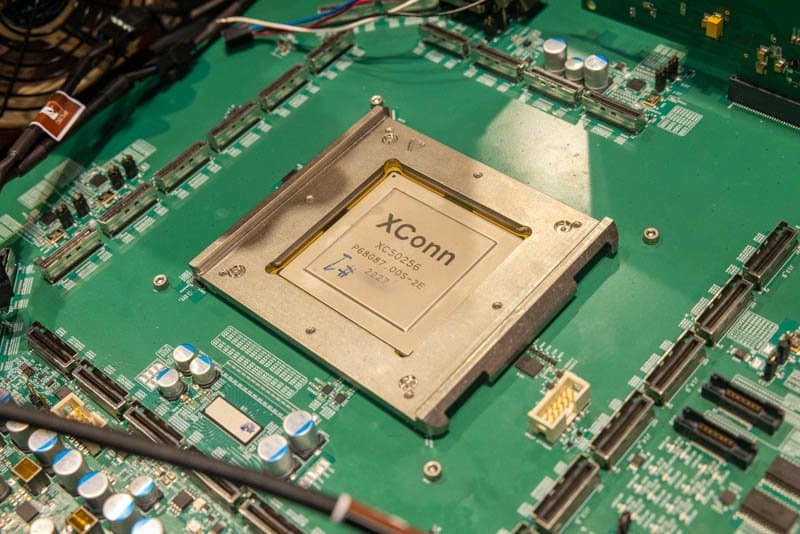

The cornerstone of XConn's technology is the XC50256, a 256-lane PCIe Gen5 switch chip with CXL 2.0 variants. This directly challenges Broadcom's current PCIe switching dominance, whose PLX-derived solutions max out at 144 lanes. Building such high-density switches presents significant engineering challenges due to signal integrity requirements at PCIe 5.0 speeds (32 GT/s per lane).

XConn's pipeline includes PCIe Gen6 and CXL 3.1 switches under development. The XC60064 series will support PCIe 6.0's 64 GT/s per lane specification and CXL 3.1's enhanced coherency capabilities. These advancements target hyperscale deployments where PCIe/CXL switches manage growing AI accelerator and SmartNIC topologies.

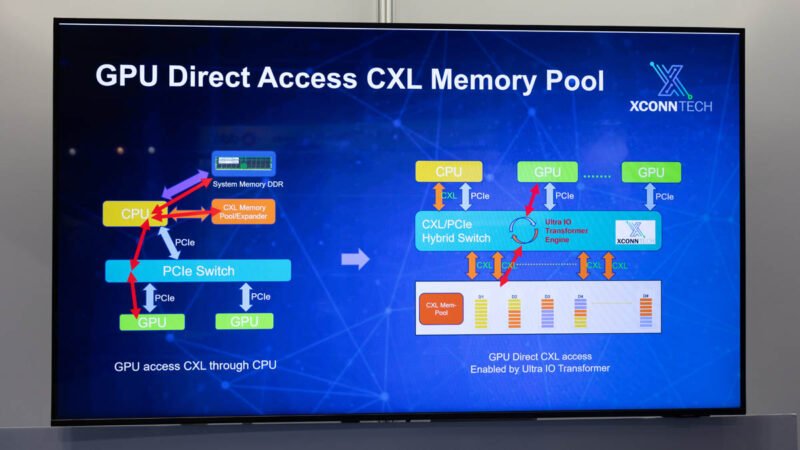

CXL memory expansion represents another critical use case. XConn's switches enable Marvell's Structera CXL Type-3 memory controllers to pool DDR resources across repurposed PCIe lanes. Hyperscalers are deploying this architecture to mitigate DDR5 supply constraints through memory compression and extended DRAM utilization cycles.

The acquisition accelerates development toward memory pooling architectures where consolidated CXL memory shelves serve multiple compute nodes. This requires PCIe/CXL switches to maintain coherency across shared memory resources while reducing duplicate data footprints. With PCIe Gen6 doubling bandwidth and CXL 3.1 enhancing resource sharing, Marvell positions itself at the intersection of next-generation memory and interconnect technologies.

Comments

Please log in or register to join the discussion