Taiwan Semiconductor Manufacturing Company (TSMC) has moved its N2 (2nm-class) process node to risk production six months ahead of schedule, signaling aggressive capacity expansion plans as Intel and Samsung ramp competing technologies.

TSMC has initiated risk production of its N2 (2nm-class) semiconductor manufacturing process ahead of schedule, with volume production now expected by late 2025 rather than early 2026 according to supply chain sources. The accelerated timeline comes as foundry competitors Intel and Samsung race to deploy their respective 18A (1.8nm-equivalent) and SF2 (2nm) nodes.

Technical Specifications and Yield Improvements

The N2 node represents TSMC's first implementation of gate-all-around (GAA) transistors, with initial wafers demonstrating:

- 18% faster switching speeds at iso-power versus N3E

- 34% power reduction at iso-performance

- 1.3x transistor density improvement (30 million transistors/mm²)

Early yield rates reportedly exceed 70% for test SRAM arrays, significantly better than the 60% yields observed at equivalent N3 development stages. The node incorporates extreme ultraviolet (EUV) lithography with 24 layers - a 33% increase over N3 - enabled by ASML's latest High-NA EUV scanners.

Supply Chain Implications

TSMC's capital expenditure for 2024-2025 has been revised upward to $44 billion, with 65% allocated to advanced nodes (N3 and below). This investment supports construction of three new fabs:

- Fab 20 in Hsinchu, Taiwan (N2 focus)

- Fab 22 Phase 6 in Tainan, Taiwan

- Arizona Fab 21 Phase 2 (delayed to 2026 due to CHIPS Act funding delays)

The accelerated timeline creates material advantages for key customers:

- Apple has secured 80% of initial N2 capacity for A19 and M5 processors

- NVIDIA booked remaining capacity through 2026 for Blackwell Next GPUs

- AMD and Qualcomm face allocation constraints until 2027 expansions

Competitive Landscape Shifts

Intel's 18A process now trails TSMC by 9-12 months based on current benchmarks:

| Metric | TSMC N2 | Intel 18A | Samsung SF2 |

|---|---|---|---|

| Density | 30M/mm² | 28M/mm² | 25M/mm² |

| Performance | 1.18x | 1.15x | 1.12x |

| Power Eff. | 1.34x | 1.29x | 1.25x |

| HVM Start | Q4 2025 | Q3 2026 | Q1 2026 |

This technological lead compounds TSMC's manufacturing scale advantage - the company currently controls 61% of global foundry revenue compared to Intel Foundry Services' 4.2% and Samsung's 11% (Q2 2024 data).

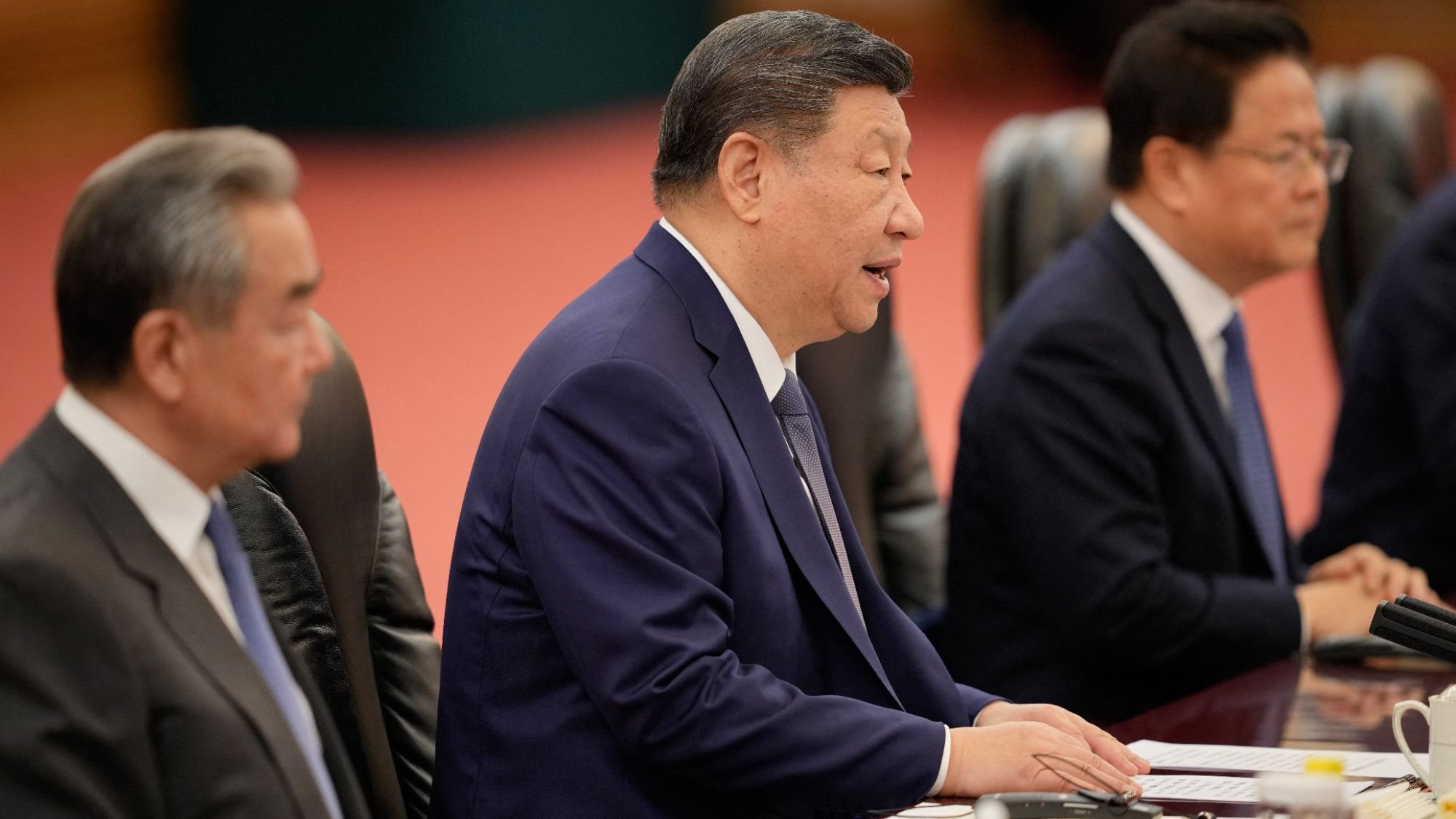

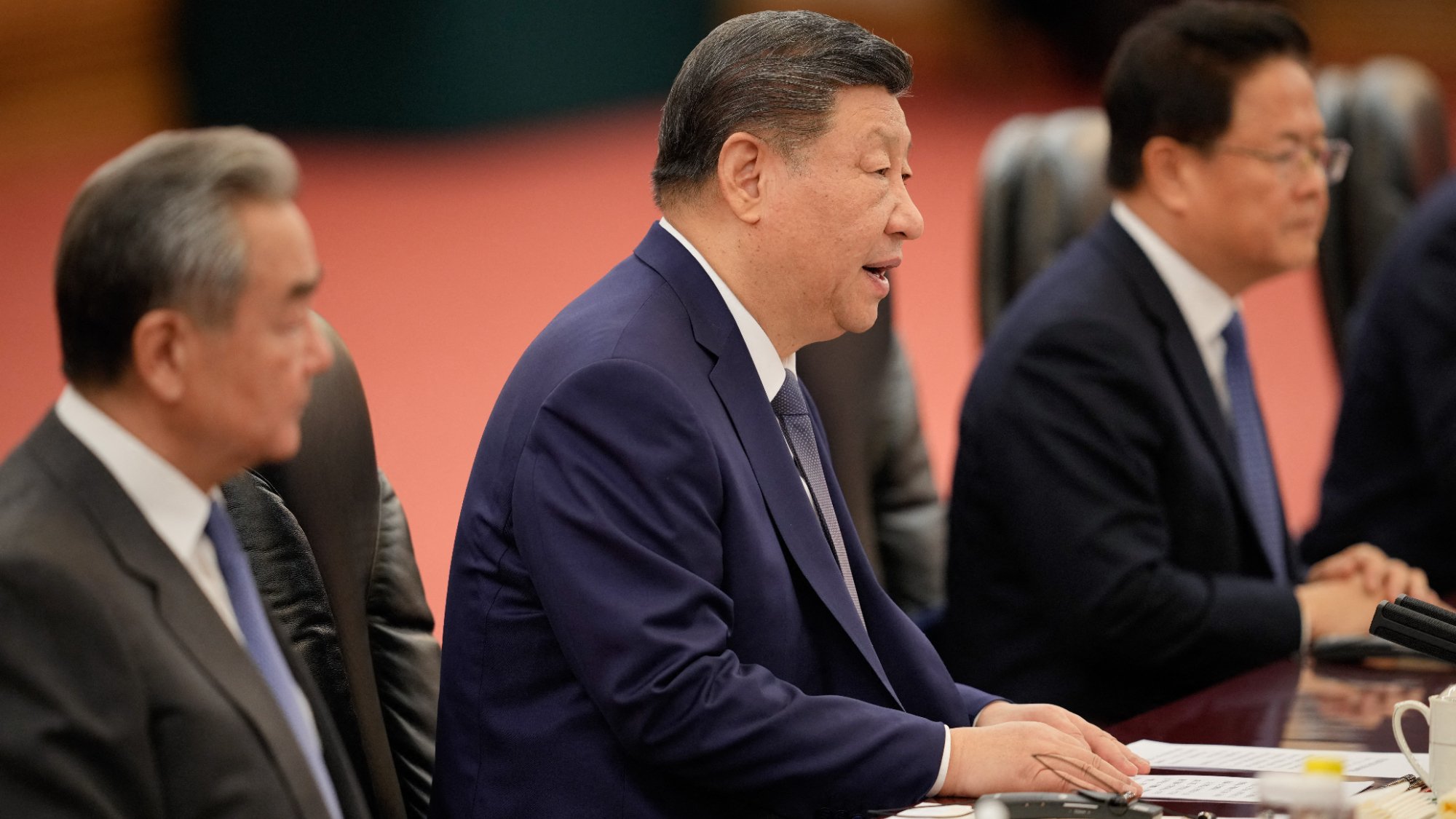

Geopolitical Manufacturing Pressures

China's SMIC continues 7nm production at 50% yields using deep ultraviolet (DUV) equipment, with its N+2 (5nm-class) node delayed until 2027 due to ASML DUV export restrictions. The U.S. Department of Commerce recently tightened licensing requirements for mature node equipment, potentially impacting 28nm capacity expansions at SMIC and Hua Hong Semiconductor.

TSMC's technology roadmap acceleration demonstrates the intensifying semiconductor manufacturing race, where process leadership now dictates not just product performance but geopolitical influence in the AI era. With N2 volume production commencing 18 months before Intel's comparable node reaches equivalent scale, the competitive gap appears widening despite U.S. industrial policy interventions.

Comments

Please log in or register to join the discussion