A detailed exploration of a project that simulates a complete computer system around a vintage 286 processor using modern hardware and software, examining the challenges of interfacing with legacy components and recreating computer architecture fundamentals.

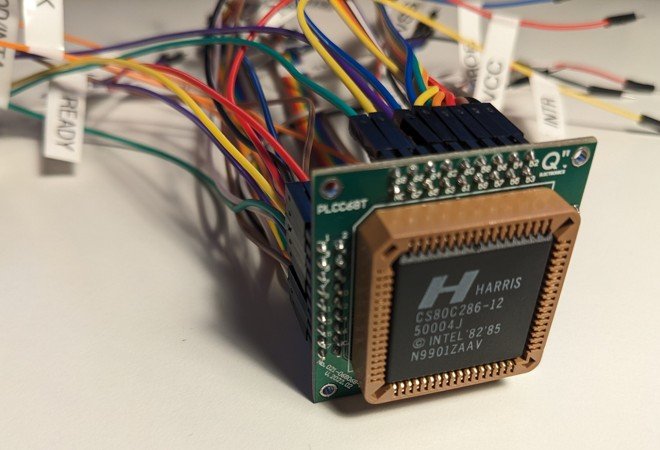

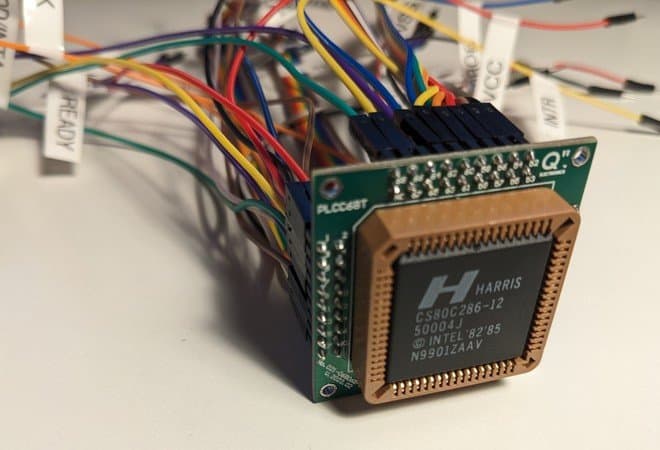

The project begins with an intriguing philosophical question about the nature of reality, referencing The Matrix, but quickly transitions to a concrete technical challenge: simulating a complete computer system around a vintage 286 processor. The author obtained a Harris 80C286-12 processor, a 1980s-era CPU that can operate at 12 MHz, and set out to recreate the surrounding hardware components using a Raspberry Pi Pico running MicroPython.

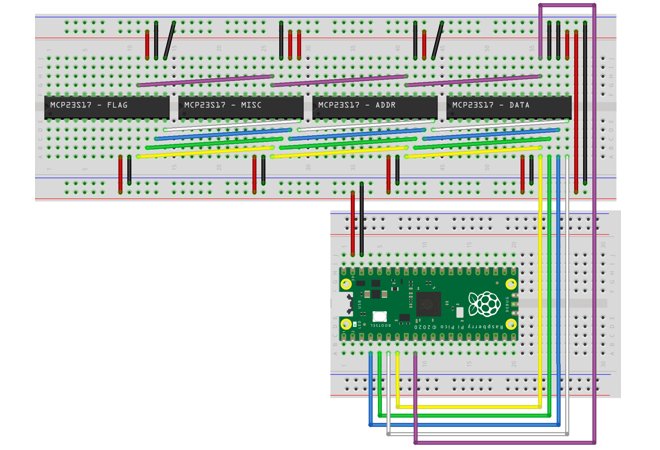

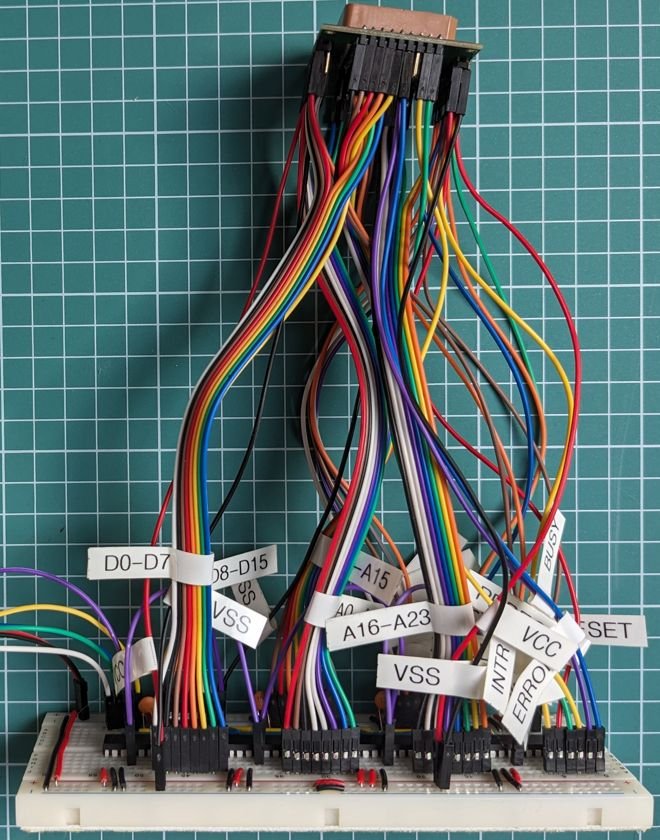

The technical challenges are immediately apparent. The 286 processor requires 57 pins for operation, far more than the Raspberry Pi Pico can directly control. To solve this, the author employs MCP23S17 IO expanders, which provide 16 configurable IO pins each. Four of these chips are needed to handle all the required connections. The author notes that while this setup can't drive the processor at its full 12 MHz speed, that limitation isn't problematic for the simulation goals.

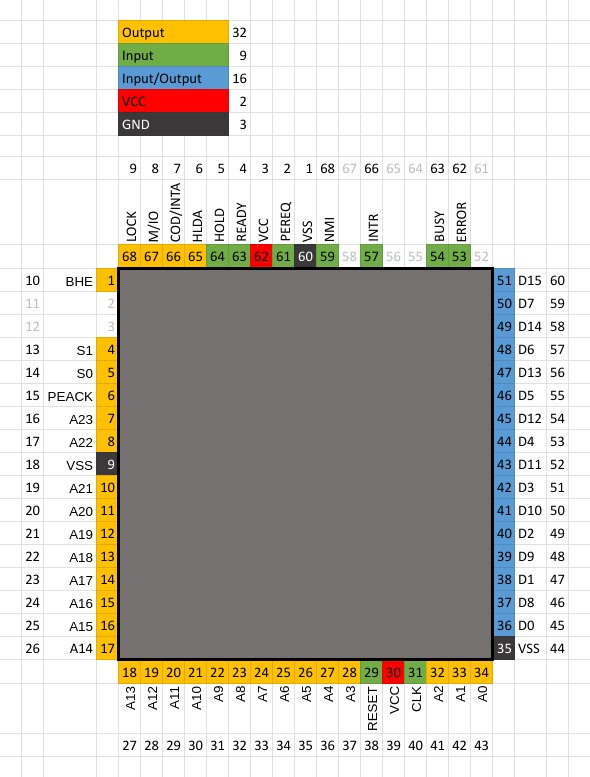

The implementation involves careful pin mapping and configuration. The processor fits into a PLCC-68 socket, which requires an adapter PCB for jumper wire connections. The author created a conversion table to manage the complex pinout and logically grouped the IO pins across the four MCP23S17 chips. The pins are divided into address lines, data lines, and control signals, with appropriate direction settings for each.

A significant challenge was configuring the MCP23S17 chips correctly. The author discovered that simply enabling hardware addressing on all chips wasn't sufficient. The configuration needed to be resent to each chip's individual hardware address, a quirk that wasn't immediately obvious from the documentation.

The initialization sequence involves several critical steps. First, the processor must be reset by holding the RESET flag active for at least 16 clock cycles, synchronized with the clock signal. After reset, the processor begins executing instructions from address 0xFFFFF0. The author's code monitors the processor's bus cycle indicators (COD/INTA, M/IO, S0, S1) to determine what operation the processor is attempting to perform.

The simulation includes a simple memory implementation using a Python dictionary. The author demonstrates the system by running assembly code that performs addition, loading the binary output from NASM (Netwide Assembler) into the simulated memory. The code handles different bus cycles (instruction read, memory read, memory write) and manages byte/word transfers according to the BHE and A0 flags.

A key insight is the little-endian nature of the 286 architecture, where bytes are stored with the least significant byte first. This affects how data is placed on the bus and how it's interpreted by the processor.

The project successfully demonstrates the execution of a simple addition program, showing the processor reading values from memory, adding them, and storing the result. The output traces each bus cycle, revealing the step-by-step execution of the assembly instructions.

This project offers valuable insights into computer architecture at a fundamental level. By simulating the interface to a vintage processor, the author demonstrates how modern microcontrollers can interact with legacy hardware and recreate essential computing functions. The work highlights the complexity of even basic computer operations and the elegance of processor design.

The project also raises interesting questions about the nature of computation. As the author notes, "for the processor, this reality is not virtual at all. It doesn't matter to it where the electrical signals are coming from, as long as they are compatible with its own internal reality." This philosophical observation connects back to the Matrix reference and underscores how computation is fundamentally about signal processing, regardless of the physical implementation.

While the project focuses on a simple 286 system, the techniques could be extended to more complex processors or even used for educational purposes to teach computer architecture. The MCP23S17 IO expander approach provides a blueprint for interfacing with other legacy hardware using modern microcontrollers.

The complete source code and detailed documentation would be valuable resources for anyone interested in similar projects. The author's troubleshooting journey, particularly the MCP23S17 configuration issue, offers practical insights that could save others time in their own implementations.

In conclusion, this project represents an impressive feat of reverse engineering and simulation, demonstrating how modern tools can be used to understand and interact with vintage computer hardware. It serves as both a technical achievement and an educational exploration of computer fundamentals.

Comments

Please log in or register to join the discussion